ПОДРОБНАЯ ИНФОРМАЦИЯ

Заявку на получение дополнительной информации по этому проекту можно заполнить здесь.

|

Номер 63-020-05 |

|||

|

Наименование проекта Устройство для решения дифференциальных уравнений |

|||

|

Назначение Для повышения точности решения дифференциальных уравнений |

|||

|

Рекомендуемая область применения В аналоговых вычислительных машинах (АВМ) |

|||

|

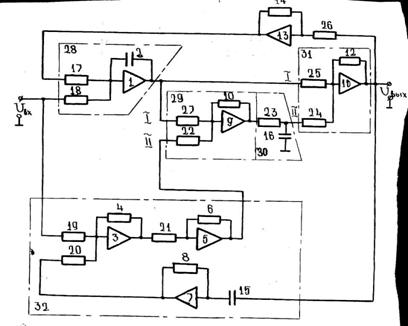

Описание 020-05 Результат выполнения технологической разработки Устройство содержит операционный усилитель 1 (см. рисунок 1) с конденсатором 2 обратной связи, операционный усилитель 3 с резистором 4 обратной связи, операционный усилитель 5 с резистором 6 обратной связи, операционный усилитель 7 с резистором 8 обратной связи, операционный усилитель 9 с резистором 10 обратной связи, операционный усилитель 11 с резистором 12 обратной связи и операционный усилитель 13 с резистором 14 обратной связи, конденсаторы 15 и 16, резисторы 17-27. Операционный усилитель 1, конденсатор 2, резисторы 17 и 18 в совокупности составляют интегратор 28, операционный усилитель 9, резисторы 10, 22 и 27 в совокупности составляют сумматор 29; резистор 23 и конденсатор 16 в совокупности составляют фильтр 30; операционный усилитель 1, резисторы 12, 24 и 25 в совокупности составляют сумматор 31, операционные усилители 3, 5 и 7, конденсатор 15 и резисторы 4, 6, 8, 19, 20 и 21 в совокупности составляют схему интегратора 32. Устройство предназначено для решения дифференциального уравнения:

Подаваемый на вход сигнал через первый 18 и третий 19 резисторы одновременно подается на две независимые параллельные цепи решения дифференциального уравнения. Входной сигналuвхпоступает на вход первого операционного усилителя, одновременно сюда же с выхода пятого операционного усилителя поступает сигнал решения дифференциального уравнения, взятый с противоположным знаком (-uвых). На первом операционном усилителе с первым конденсатором обратной связи осуществляется интегрирование и интервирование суммарного сигнала. Сигналu1cвыхода первого операционного усилителя представляет собой сумму сигнала ошибки решения дифференциального уравнения методом понижения порядка производной и сигнала решения дифференциального уравнения, взятую с противоположным знаком. При интегрировании высокочастотная ошибка гасится, но происходит усиление низкочастотной составляющей ошибки. Через третий резистор 13 входной сигналuвхтакже поступает на вход второго операционного усилителя 3. Одновременно на вход второго операционного усилителя 3 через пятый резистор 20 поступает сигнал с выхода четвертого операционного усилителя 7 и т. д. Величина ошибки решения дифференциального уравнения методом понижения порядка производной на выходе первого операционного усилителя в предлагаемом устройстве меньше, чем в существующих. Это происходит потому, что на вход усилителя 1 через второй резистор 17 поступает сигнал не с выхода первого операционного усилителя, а с выхода устройства через инвертор, состоящий из девятого резистора 26 и пятого операционного усилителя 13 с десятым резистором 14 обратной связи. Сигнал на выходе операционного усилителя 13 представляет собой сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения, взятую с обратным знаком: -(uвых+

Аналогично на выходе третьего операционного усилителя 5 имеем сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения методом повышения порядка производной, причем ошибка меньше, чем у прототипа. Действительно, если сигнал на конденсатор 15 в прототипе подавался с выхода третьего операционного усилителя, то в предлагаемом устройстве на конденсатор 15 подается с выхода устройства. Так как ошибка решения дифференциального уравнения на выходе устройства меньше ошибки решения дифференциального уравнения методом повышения порядка производной, то и ошибка на выходе третьего операционного усилителя 5 меньше аналогичной ошибки в прототипе. Уменьшение ошибок на выходе двух параллельных цепей решения дифференциальных уравнений в свою очередь приводит к уменьшению ошибки на выходе устройства.

Рис. 1. Принципиальная схема устройства для решения дифференциальных уравнений |

|||

|

Преимущества перед известными аналогами Наличие в схеме устройства дополнительного отрицательного усилителя и двух токозадающих конденсаторов позволяет повысить точность решения дифференциальных уравнений |

|||

|

Стадия освоения Внедрено в производство |

|||

|

Результаты испытаний Технология обеспечивает получение стабильных результатов |

|||

|

Технико-экономический эффект Годовой экономический эффект от внедрения составил 10 млн. рублей |

|||

|

Возможность передачи за рубеж Возможна передача за рубеж |

|||

|

Дата поступления материала 25.01.2005 |

Инновации и люди

У павильонов Уральской выставки «ИННОВАЦИИ 2010» (г. Екатеринбург, 2010 г.)

Мероприятия на выставке "Инновации и инвестиции - 2008" (Югра, 2008 г.)

Открытие выставки "Малый бизнес. Инновации. Инвестиции" (г. Магнитогорск, 2007 г.)

Демонстрация разработок на выставке "Малый бизнес. Инновации. Инвестиции" (г. Магнитогорск, 2007 г.)